盡管 QFN 有這麼多的優點,但它卻給電路板組裝廠帶來不少的焊接品質衝擊,因為 QFN 為無引腳設計,一般很難從其外觀的焊錫點來判斷其焊錫性是否良好,雖然 QFN 的封裝側面仍留有焊腳,但幾乎都是 Leaf frame(導線架)的切斷面,並無電鍍處理,所以很難吃錫。

▲▼ QFN 的側面焊腳為導線架(lead frame)的切斷面,並無墊鍍層。

QFN 吃錫標準

在 IPC-A-610D, Section 8.2.13 Plastic Quad Flat Pack No Leads (PQFN) 的規範中,並未定義 QFN 側邊吃錫一定要有平滑的凹形曲線。

There are some package configurations that have no toe exposed or do not have a continuous solderable surface on the exposed toe on the exterior of the package and a toe fillet will not form.

事實上 QFN 真正的吃錫部份應該是在底部邊框的焊腳與正底部的散熱片,底部焊腳有點像 BGA,所以應該可以參考 IPC-A-610D, Section 8.2.12 Plastic BGA 的標準。

▼ QFN側邊焊腳吃錫不好,但電氣特性仍然良好。

▼ QFN側邊焊腳吃錫良好。

QFN 焊錫性檢查及測試

就如同 BGA 的焊錫檢查標準,目前 QFN 的焊錫檢查除了用電測 (In-Circuit-Test 、 Function Test) 來偵測其功能之外,一般也會佐以光學儀器或 X-ray 來檢查焊錫的開、短路不良現象。老實說 X-Ray 的等級不夠好的話,還真的不是很容易檢查出來 QFN 的焊錫問題。如果無論如何還是找出焊錫性的問題,最後只好使用切片(Micro-section)或 滲透染紅試驗(Red Dye Penetration Test)等破壞性實驗來檢查。

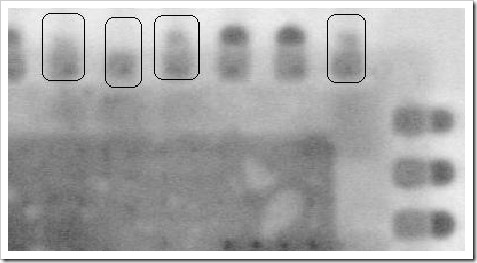

▼這張圖片來自網路,使用 X-Ray 檢查 QFN 焊錫。

▼這張圖片來自網路,使用 X-Ray 檢查 QFN 焊錫,疑似焊接不良。

QFN 空焊的可能解決方法

QFN 空焊時應該先澄清是否為零件氧化問題,可以把零件拿去作一下沾錫性實驗以作確認,再來要判斷是否有固定焊腳空焊,一般接地腳比較容易產生空焊,可以考慮變更電路板的佈線設計,在電路板的線路(trace)上增加熱阻以減少焊腳直接接地的面積,這樣可以延緩熱量散失的速度。

也可以試著調整爐溫(reflow profile),或改為斜升式迴流焊曲線(slumping type)以減少錫膏在預熱時吸收過多的熱量。

曾經發現 QFN 底部中間的接地焊墊上的錫膏印刷過多,過迴流焊時造成零件浮起的空焊,另外也要留意將 QFN 底部中間的接地焊墊印刷成「田」字型會比整片印刷要來得好,過迴流焊時也較不會因錫膏全部熔融成一團而造成零件浮動的情形。

另外電路板的焊墊上盡量不要有通孔(vias),中間散熱接地墊上的通孔(vias)也要盡量塞孔,否則容易影響焊錫量及氣泡的產生,嚴重的還可能導至焊接不良。

▲ 通孔(vias)塞孔

加「氮氣」是否可以有效增加 QFN 的良率?我只能說見仁見智,氮氣是可以防止零件氧化,但能否焊上 QFN 的側面焊腳,還是有待觀察,況且加氮氣會增加成本,還是擺在最後再考慮就好了。

以上是個人對 QFN 的瞭解與看法,如有不同意見、看法,歡迎留言討論…

相關閱讀:

如何挑選錫膏(Solder paste selection)

Vias-in-pad(導通孔在墊)的處理原則

介紹認識【錫膏(solder paste)】的基本知識

0 意見:

張貼留言